## MAE140 - Linear Circuits - Fall 09 Midterm, November 10

#### Instructions

- (i) This exam is open book. You may use whatever written materials you choose, including your class notes and textbook. You may use a hand calculator with no communication capabilities

- (ii) You have 70 minutes

- (iii) Do not forget to write your name, student number, and instructor

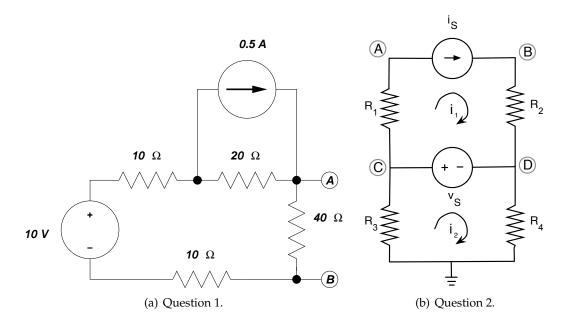

Figure 1: Circuits for questions 1 and 2.

### 1. Equivalente Circuits

- **Part I** [4 points] Use source transformations and association of resistors to find the Thevenin equivalent to the circuit in Fig. 1(a) as seen from terminals A and B.

- **Part II** [4 points] A classmate was arguing with you that one would "extract" the most power out of this circuit by connecting a very small resistance between terminals A and B. You argued that he/she was wrong and that a 20 Ω resistor would be a better choice. Who is right and why? *Hint #1: Don't complicate: all you need to do is compare the two options! Hint #2: Use the Thevenin equivalent computed in Part I to answer the question.*

#### Solution:

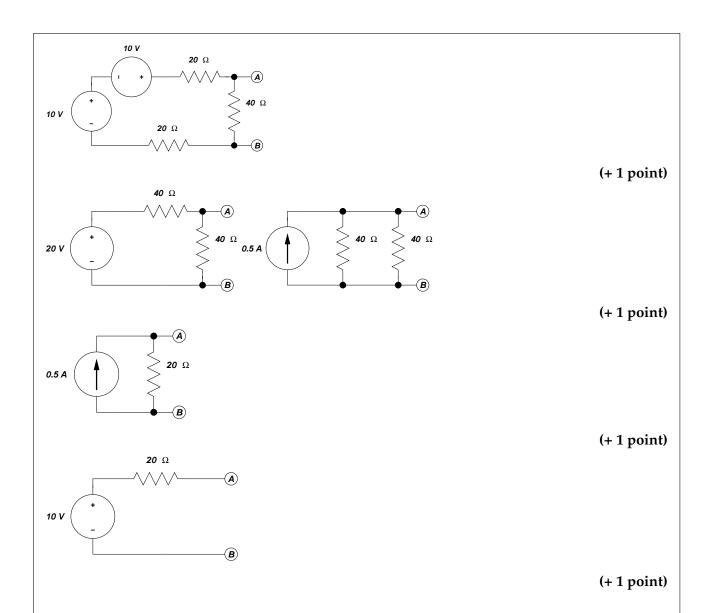

Part I: A possible series of source transformations is shown here:

**Part II:** Let's investigate the two scenarios. In the case of a small resistance, say  $R = \epsilon \Omega$ , using the Thevenin equivalent and voltage division we have that

$$v_R = \frac{\epsilon}{20 + \epsilon} 10 \approx \epsilon/2 \text{ V},$$

$i_R = v_R/\epsilon \approx 1/2 \text{ A},$  (+ 1 point)

The power absorbed by the small resistor is then

$$p_R = v_R i_R \approx \epsilon / 4 \,\mathrm{W}.$$

which is close to zero when  $\epsilon$  is small.

When  $R = 20 \Omega$ , using the Thevenin equivalent and voltage division we have that

$$v_R = \frac{20}{20+20} 10 = 5 \text{ V},$$

$i_R = v_R/20 = 1/4 \text{ A}.$  (+ 1 point)

(+ 1 point)

The power absorbed by the  $20~\Omega$  resistor is then

$$p_R = v_R i_R \approx 5/4 \,\mathrm{W}.$$

That is, you were right :).

(+ 1 point)

It turns out this is the maximum power that this circuit can deliver to a load, but we did not cover that. See T R & T Chapter 3.

# 2. Mesh Current and Node Voltage Analysis

- **Part I** [4 points] Formulate mesh-current equations for the circuit in Figure 1(b). Use the mesh currents shown in the figure and clearly indicate how you handle the presence of a current source, the final equations, and the unknowns they must be solved for. **Do not modify the circuit or the labels**. No need to solve any equations!

- Part II [4 points] Formulate node-voltage equations for the circuit in Figure 1(b). Use the node labels provided in the figure and clearly indicate how you handle the presence of a voltage source, the final equations, and the unknowns they must be solved for. Do not modify the circuit or the labels. No need to solve any equations!

Hint: Use a supernode

- **Part III** [1 bonus point] If you were allowed to select the ground node in the circuit of Figure 1(b), describe what would you do in order to avoid having to use a supernode in Part II? **Do not write or solve any equations**!

# Solution:

**Part I:** The current source only belongs to a single mesh, so we can easily take care of it by using method 2. In other words, we set

$$i_1 = i_S.$$

(+ 1 point)

Next, we write KVL for the other mesh by inspection

$$(R_3 + R_4)i_2 = -v_S$$

(+ 1 point)

The negative sign in front of  $v_s$  is because the voltage source is not assisting the mesh current.

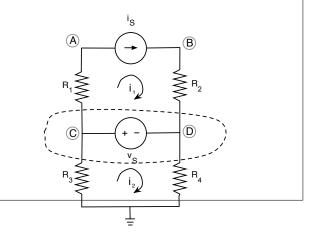

**Part II:** The voltage source is not in series with a resistor, so we cannot use source transformation to take care of it. Also, the ground node has already been chosen for us, so we cannot invoke it to take care of the voltage source.

Therefore, we need to use method 3, i.e., we need to create a supernode C-D, as indicated in the figure on the right.

[1 point]

We can now take care of the voltage source with the supernode by setting

$$v_C - v_D = v_S \tag{+1 point}$$

Next, we write KCL for the supernode,

$$G_1(v_C - v_A) + G_2(v_D - v_B) + G_3v_C + G_4v_D = 0$$

(+ 1 point)

KCL at node A yields

$$G_1(v_A - v_C) + i_S = 0$$

(+.5 point)

and KCL at node B yields

$$G_2(v_B - v_D) - i_S = 0$$

(+ .5 point)

This gives us a total of 4 equations in the 4 unknowns  $v_A$ ,  $v_B$ ,  $v_C$ , and  $v_D$ .

**Part III:** If we were allowed to choose ground, we could either set it at node C or D. Any of these two options would automatically take care of the voltage source. Setting up nodal analysis after this would be easy because the remaining independent source would be a current source. (1 **point**)

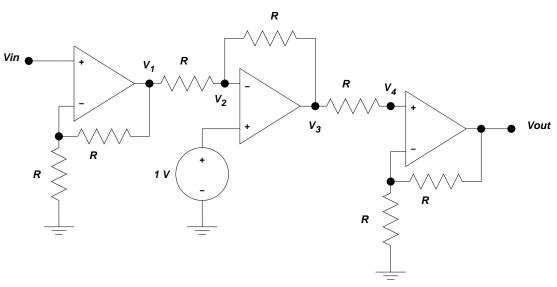

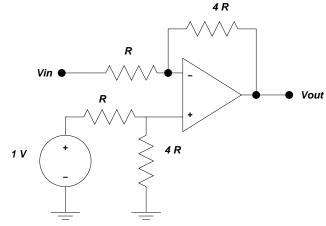

Figure 2: Circuit for question 3.

## 3. Operational Amplifier Analysis and Design

**Part I** [4 points] Determine all voltages indicated in the circuit of Figure 2 in terms of *V*<sub>in</sub>. Use these voltages to show that it realizes the following function:

$$V_{\rm out} = 4(1 - V_{\rm in}).$$

**Part II** [4 points] Design a circuit using a single OpAmp that would realize the exact same function using a single 1 V source. Name one advantage/disadvantage of your design versus the design of Figure 2.

### Solution:

**Part I:** Most of the circuit is standard with the exception of the 1 V source connected to the '+' terminal of the second opamp stage. So if we label the voltages as in the figure, we have, using the non-inverting opamp gain,

$$V_1 = \frac{R+R}{R} V_{\rm in} = 2V_{\rm in},$$

$V_{\rm out} = \frac{R+R}{R} V_4 = 2V_4,$  (+ 1 point)

Also, from KCL at the '-' terminal of the second opamp,

$$\frac{V_2 - V_3}{R} = \frac{V_1 - V_2}{R}$$

(+ 1 point)

which can be rearranged as

$$V_3 = 2V_2 - V_1$$

Because  $V_2 = V_N = V_P = 1$  V we have that

$$V_3 = 2 - V_1 = 2 - 2V_{\rm in}$$

(+ 1 point)

Finally,  $V_4 = V_3$  because there is a zero current going into the '+' terminal of the opamp. Summarizing:

$V_1 = 2V_{\rm in},$   $V_2 = 1V,$   $V_4 = V_3 = 2 - 2V_{\rm in}$  (+ 1/2 point)

Hence

$$V_{\text{out}} = 2V_4 = 4 - 4V_{\text{in}}.$$

(+ 1/2 point)

**Part II:** A standard subtractor would do the job, that is the following circuit (+ 2 points)

Note that this is very similar to the circuit in the middle of Figure 2. This circuit has gains

$$V_{\text{out}} = \frac{4R}{4R+R} \frac{4R+R}{R} 1 \,\text{V} - \frac{4R}{R} V_{\text{in}} = 4 - 4V_{\text{in}} \qquad (+1 \text{ point})$$

One disadvantage is that the input impedance as seen from  $V_{in}$  is not large, potentially loading the input circuit. (+ 1 point)